Przykład magistrali systemowej

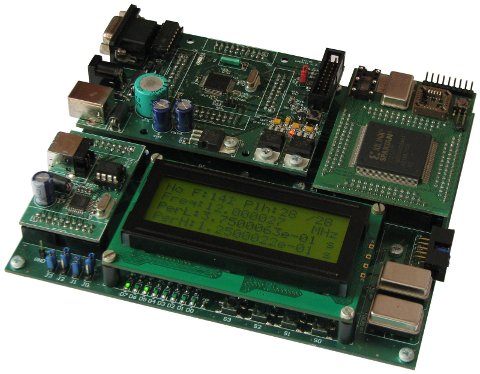

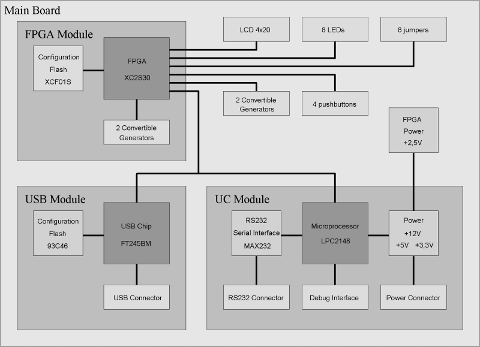

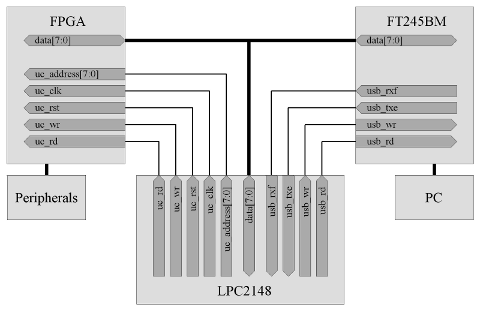

W przykładowym układzie jako magistralę zewnętrzną, łączącej mikroprocesor z FPGA i modułem USB, zdecydowano się na klasyczną synchroniczną magistralę adresowo-danych z dodatkowym sygnałem zerującym. Omawianym układem jest system lpc_xc2s_ftdi którego wygląd i schemat blokowy przedstawiono na rysunkach 1 i 2:

Jak widać jest to prosta i wydajna magistrala. Jedyną jej wadą jest stosunkowo duża ilość zajmowanych bitów co może niekiedy być źródłem problemów. Jako alternatywę można użyć prostego interfejsu SPI i komunikację z modułem oprzeć na wbudowanym w mikrokontroler kontrolerze Host-SPI. Jednak zaprojektowanie Device-SPI wewnątrz układu FPGA wcale nie jest takie łatwe, a ze względu na szeregowy charakter magistrali prędkości transmisji również nie należy do najszybszych. Godnym uwagi pomysłem jest połączenie magistrali danych i adresowej na zasadach podobnych jak to ma miejsce w modułach LCD 2x16 i układach pamięciowych takich jak NAND-Flash [1]. Przez takie połączenie uzyskiwane jest zmniejszenie ilości zajmowanych bitów przy jednocześnie niewielkim spadku prędkości.

W tym przypadku najlepszym połączeniem okazało się rozwiązanie z osobną magistralą adresową i danych. Za tym rozwiązaniem przemawia również fakt, że magistrala danych jest współdzielona z układem odpowiedzialnym za transmisję USB, co przy połączeniu z magistralą adresową utrudniłoby transmisje DMA pomiędzy modelem a układem USB. Zrealizowany na tym urządzeniu przykładowy układ okresomierza i częstościomierza nie wymaga dużych transferów danych, jednak projektując system postawiono na uniwersalność rozwiązania. Innym czynnikiem który zadecydował o wyborze magistrali jest duży zapas niewykorzystanych pinów w układach mikrokontrolera i układu FPGA.

Główna magistrala danych systemu przedstawiona została na rysunku:

Jak widać na rysunku 3, do komunikacji mikrokontrolera LPC2148 z FPGA użyto następujących linii sterujących:

- uc_clk. Sygnał taktujący wszelkie operacje zapisu odczytu przeprowadzane pomiędzy mikrokontrolerem LPC2148 a układem FPGA

- uc_rst. Sygnał zerujący. Gdy ten sygnał jest ustawiony to następuje ustawienie do wartości początkowej wszystkich wewnętrznych rejestrów procesora. Sygnał zerujący musi trwać przynajmniej jeden cykl zegarowy

- uc_wr. Sygnał określający kierunek wymiany danych. Mikrokontroler zapisuje dane do układu FPGA

- uc_rd. Sygnał określający kierunek wymiany danych. Mikrokontroler odczytuje dane z układu FPGA

- uc_address. Magistrala adresowa, wskazuje rejestr wewnętrzny w układzie FPGA na którym będzie przeprowadzona operacja zapisu/odczytu

- data. Magistrala danych. Współdzielona z interfejsem USB.