Połączenie Mikrokontroler - USB

W zaprojektowanym układzie mikrokontroler może komunikować się z układem odpowiedzialnym za wymianę danych pomiędzy urządzeniem pomiarowym a komputerem PC. W układzie użyto układu FT245BM firmy FTDI o asynchronicznym interfejsie wymiany danych. Znaczenie sygnałów modułu USB jest następujące:

- usb_rxf. Sygnał informujący o danych w module USB, które są do odebrania przez mikrokontroler

- usb_txe. Sygnał informujący o możliwości przyjęcia przez moduł USB kolejnych danych do wysłania do komputera PC

- usb_wr. Sygnał żądania zapisu danych do modułu USB

- usb_rd. Sygnał żądania odczytu z modułu USB

- data. Magistrala danych

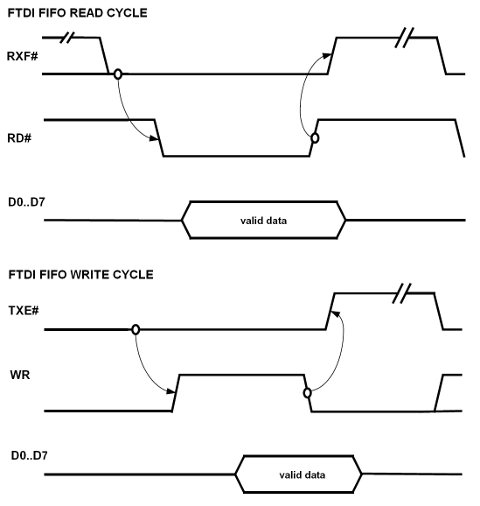

Na rysunku 4 przedstawiono przebieg sygnałów przy zapisie i odczycie danych do i z układu USB FT245BM przez mikrokontroler:

Rys 4. Wykresy czasowe operacji odczytu i zapisu dla modułu USB

Zależności czasowe przedstawionych przebiegów dostępne są w dokumentacji układu FT245BM [3].

Fragment kodu źródłowego umożliwiającego komunikację mikrokontrolera

z rejestrami modelu urządzenia pomiarowego przedstawiono na listingu 1:

always@(posedge uc_clk)

begin

if (sys_rst == 1'b1)

begin

//resetowanie_sygnalow_wewnetrznych

end

else

case (uc_adr)

Adres_A:

begin

dane_dla_uc <= rejestr_wewnetrzny_X;

end

Adres_B:

begin

dane_dla_uc <= rejestr_wewnetrzny_Y;

if (uc_wr_n == 1'b0)

begin

rejestr_wewnetrzny_Z <= dane_z_uc;

end

end

endcase

end

Poza znanymi już konstrukcjami języka Verilog komentarza wymagają konstrukcje ściśle powiązane z przykładowym interfejsem przedstawionym na listingu 1.

Zasadę zaprezentowanego modułu można opisać w następujący sposób:

- sys_rst == 1'b1. W przypadku aktywnego sygnału zerującego sys_rst wszystkie rejestry wewnętrzne ustawiane są do wartości początkowej. W przeciwnym przypadku układ pracuje wg ustalonego algorytmu

- Adres_A, Adres_B. W zależności od pojawienia się któregoś z tych adresów na magistrali adresowej modułu, wykonywany zostaje kod zawarty pomiędzy słowami kluczowymi begin/end

- dane_dla_uc <= rejestr_wewnetrzny_Y. Dane z rejestru wewnętrznego przepisywane są do rejestru wyjściowego modułu. W tym przypadku nie jest konieczne badanie stanu sygnału uc_rd, ponieważ na wyjściu układu znajduje się zespół 8 bramek trójstanowych, które wystawiają zawartość rejestru dane_dla_uc tylko w przypadku gdy sygnał uc_rd jest aktywny

- rejestr_wewnetrzny_Z. Rejestr modułu pomiarowego, który nadpisywany jest wartością rejestru dane_z_uc w przypadku, gdy adres uc_adr i sygnał zapisu uc_wr mają odpowiednie wartości [4].