Parametry płyty

Parametry płyty

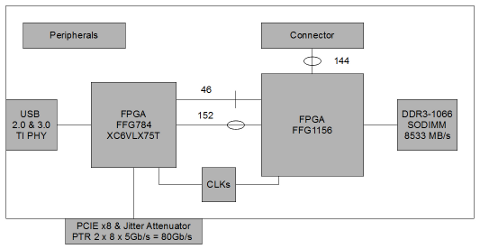

Budowa płyty to dwa układy FPGA firmy Xilinx z serii Virtex-6. Interfejs PCI-Express 2.0, Interfejs USB Super Speed 3.0 i interfejs DDR3-1066. Pozostałe peryferia mają charakter pomocniczy. Uproszczony schemat płyty przedstawiono na rysunku:

Projekt płyty to 16-sto warstwowa płyta PCB która zawiera dwa układy FPGA firmy Xilinx oraz peryferia które razem tworzą system o następującej konfiguracji:

- Główny (ale nie największy) układ FPGA to XC6VLX75T-2FF784C. Jest to centralny układ FPGA zapewniający komunikację z otoczeniem poprzez interfejsy USB i PCIE oraz odpowiedzialny jest za dynamiczną rekonfigurację drugiego układu FPGA pełniącego rolę właściwego układu obliczeniowego akceleratora

- Układ obliczeniowy to XC6VLX240T-2FFG1156 lub inny w kompatybilnej obudowie 1156 kulkowej. Odpowiedzialny za wykonywanie właściwej akceleracji zadanych obliczeń. Do układu bezpośrednio połączony jest interfejs pamięci DDR3 oraz interfejs złącza zewnętrznego używanego do podpięcia adapterów usprawniających proces symulacji

- USB3.0 Device. Warstwa fizyczna TUSB1310A wspierająca tryby pracy USB Super-Speed (5Gb/s) oraz standardowo interfejsy wolniejsze

- PCIE x8. Interfejs do magistrali PCI-Express. Płytę zaprojektowano do wspierana standardu 2.0 o szerokości 8 par nitek sygnałowych

- Moduł pamięci DDR3 SODIMM o pełnym podpięciu wszystkich linii modułu do układu FPGA. Przepustowość połączeń zaprojektowane do wspierania najszybszych transferów oferowanych przez dostępne na rynku moduły pamięci ograniczonych jedynie wydajnością układu FPGA

- Interfejsy użytkownika i systemowy wymiany danych pomiędzy układami FPGA. Interfejs użytkownika to 76 linii różnicowych projektowanych przede wszystkim jako 76 bardzo szybkich linii z interfejsem LVDS, które mimo wszystko mogą pracować jako linie single-ended dostarczając wówczas 152 linii łączących obydwa układy. Interfejs systemowy to dedykowany 46-liniowy interfejs akceleratora podpięty do linii systemowych obliczeniowego układu FPGA. W przypadku różnicowych linii LVDS każda z nich pracująca jako DDR LVDS ma prędkość transmisji 1,3Gb/s

- Zewnętrzny interfejs w postaci złącz oferujący interfejs wymiany danych pomiędzy obliczeniowym układem FPGA a zewnętrznymi adapterami. Ilość linii dla single-ended to 144 oraz 77 dla LVDS

- CLK’s. System zegarów zapewniający taktowanie układów FPGA i innych peryferii. Zastosowano zestaw konfigurowalnych i stałych zegarów. Dodatkowo na potrzeby PCIE oraz USB3.0 zastosowano tłumiki jitter'a. Zastosowane zegary umożliwiają uzyskanie zegarów w zakresie częstotliwości do 700MHz

- Peripherals. Podstawowe peryferia takie jak DIP-Switch'e, Diody LED i jumpery na potrzeby ustawień konfiguracyjnych i monitorowania stanu pracy systemu

- Zasilanie. Płytę wyposażono w 10 konwerterów napięć z których najbardziej wydajnym jest 22-amperowy moduł 1V

Interfejsy:

- Wersja do wydruku

- Zaloguj się, by odpowiadać