Timing Constraints

Timing Constraints. Jest to opcja, która informuje jaką częstotliwość pracy modułu spodziewamy się osiągnąć dla każdego z wejść zegarowych. Należy jednak pamiętać, że zbyt duża wartość wygeneruje błąd lub ostrzeżenie podczas wykonywania implementacji. Opcja ta jest dostępna na panelu projektu przedstawionym na rysunku

Panel programu WebPACK poprzez kliknięcie lewym przyciskiem myszki na pole:

Create Timing Constraints

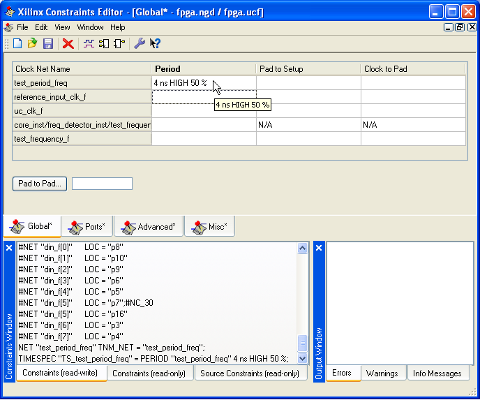

W tym momencie wykona się synteza modelu oraz początkowa część implementacji. Gdy wszystko będzie przebiegać zgodnie z planem, pojawi się nowa aplikacja w której należy wybrać zakładkę Global i wprowadzić oczekiwaną wartość podaną w nanosekundach. Patrz rysunek poniżej. Bez tego parametru, narzędzie przestaje optymalizować układ dużo wcześniej niż umożliwiają mu na to jego algorytmy.

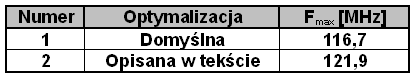

W przypadku modelu częstościomierza przed i po zastosowaniu opisanych ustawień narzędzia uzyskano następujące wyniki:

Maksymalna częstotliwość pracy modelu FPGA

Na podstawie danych z tabeli 3 można stwierdzić, że nawet dla prostego przykładowego modelu częstościomierza, który zajmuje bardzo mało zasobów układu FPGA, poprawa maksymalnej częstotliwości pracy jest zauważalna. Niekiedy jednak zaznaczenie opisanych ustawień powoduje, że przy kilku domenach zegarowych, interesująca nas domena zegarowa będzie pracowała wolniej niż przez załączeniem dodatkowych funkcji optymalizacyjnych. W większości przypadków zaproponowane ustawienia narzędzia powodują znaczne przyśpieszenie pracy projektowanego układu. Test na innym znacznie bardziej rozbudowanym modelu (Analizator Stanów Logicznych) wykazał, że maksymalna częstotliwość pracy wzrosła ze 140MHz dla domyślnych ustawień do 214MHz po załączeniu opisanych w tym rozdziale ustawień.

Narzędzie WebPACK jest darmowym oprogramowaniem. Istnieją również narzędzia innych firm, niestety już dostępne odpłatnie, które syntezują model do niekiedy znacznie wydajniejszej postaci niż robi to wbudowany w WebPACK syntezer. Warto o tym pamiętać przy projektowaniu profesjonalnych urządzeń opartych o układy FPGA.

Pozycje wykorzystane jako dodatkowe źródła informacji:

- [x] Dokumentacja programu ISE WebPack

Autorem artykułu jest mgr inż. Krzysztof Fijak