Kodowanie licznika

W przypadku licznika pomiarowego użytego w projekcie częstościomierza, również miała miejsce sytuacja pogorszenia się otrzymanych parametrów modelu po zastosowaniu ogólnych zaleceń projektowych. Ta uwaga jest o tyle ważna ponieważ udowadnia znaną powszechnie tezę, że doświadczenie stanowi jeden z najistotniejszych czynników decydujących o powodzeniu projektów.

Do tej pory zwrócono uwagę na rozbieżności w implementacjach maszyny stanów w odniesieniu do zalecanych reguł kodowania a osiągniętymi wynikami. Obecnie zajmiemy się dokładniejszą analizą licznika pomiarowego użytego w przykładowym częstościomierzu.

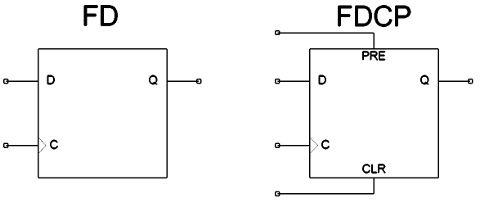

W układzie FPGA dostępnych jest kilka wersji przerzutnika D. Podstawowe dwa to FD i FDCP pokazane na rysunku:

Przerzutniki D stosowane w układach FPGA [1]

Podczas tworzenia przykładowego częstościomierza zdecydowano się na wybór licznika bez wejść zerująco-ustawiających. Elementarnym zaleceniem przy projektowania modeli jest zalecenie o unikaniu konstrukcji asynchronicznych. Używając asynchronicznego zerowania bardzo często pogarszają się wskaźniki:

- Rozmiar modelu

- Maksymalna częstotliwość pracy modelu

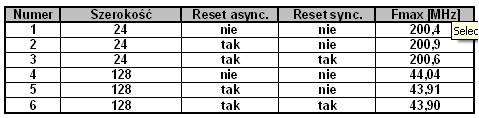

Kierując się tymi zaleceniami, użyto przerzutnik FD. Wyniki z syntezy poszczególnych przedstawiono w tabeli:

Maksymalna częstotliwość pracy liczników synchronicznych

Jak widać, nie ma praktycznie żadnej różnicy pomiędzy zastosowanymi rozwiązaniami. Mimo, że licznik z synchronicznym resetem posiada więcej logiki to jego prędkość działania jest identyczna z prędkością pozostałych konstrukcji. Dlatego tez podczas projektowania np. liczników warto dostosować się do zaleceń o stosowaniu synchronicznego zerownia. Pomimo, że nie jest to zgodne z wynikami przeprowadzonego testu, to konieczność zastosowania dodatkowej logiki może znacząco zmienić uzyskiwane parametry modelu. Podobnie jak to miało miejsce przy wyborze maszyny stanów, to i w tym przypadku należy do każdego problemu podejść indywidualnie.

Podsumowanie i literatura

Pozycje wykorzystane bezpośrednio do opracowania treści artykułu:

- [1] Xilinx Libraries Guide. Wydanie 8.2i

Autorem artykułu jest mgr inż. Krzysztof Fijak