Kodowanie maszyny stanów

Przy projektowaniu modeli takich jak częstościomierze, analizatory stanów logicznych itp można wybrać spośród wielu szkieletów konstrukcji, które można zaimplementować na wiele różnych sposobów. Spośród dostępnych wybrano te, które demonstrują jak ogólne zalecenia projektowe nie zawsze się sprawdzają. Należą do nich:

- Kodowanie maszyny stanów

- Użycie różnych wersji przykładowego licznika pomiarowego

W przypadku kodowania maszyny stanów, problem zaprojektowania szybkiego rozwiązania sprowadza się m.in. do właściwego wybrania implementowanej maszyny stanów. Projektant może zdecydować się na jedną z wielu kombinacji możliwych do zaimplementowania w układach FPGA. W pierwszej kolejności należy zdecydować się automat Mealy’ego lub Moore’a, który to na ogół lepiej sprawdza się w układach FPGA [6]. Dokładniejszy opis automatów stanów, innych konstrukcji symulacyjnych jak i syntezowanych oraz ogólne zalecenia projektowe znaleźć można w pomocy programu WebPack oraz w „Language Templates” dostępnych w programie WebPack w miejscu:

Menu->Edit-> Language_Templates

Maszyny stanów przedstawiono w miejscu:

Menu->Edit-> Language_Templates-> Verilog-> Synthesis_Constructs-> Coding_Examples-> State_Machines

Jako przykładowy projekt wybrano częstościomierz którego automat stanów został przedstawiony na rysunku:

W przykładowym projekcie zdecydowano się na automat Moore’a, co nie jest najistotniejszym przedmiotem analizy w tym artykule. Dla analizy optymalizacji czasowej dużo bardziej interesującym zagadnieniem jest sposób zakodowania danej maszyny stanów który można zrealizować w następujący sposób:

- One-Hot lub Binary. W przypadku One-Hot tyle ile jest stanów w maszynie taka jest szerokość rejestru, który decyduje o aktualnie wykonywanym stanie. W trybie binarnym stosowane jest zwykłe kodowanie dwójkowe. Na ogół kodowanie One-Hot jest szybsze

- Fast lub Save. W przypadku Fast nie zakłada się, ze automat stanów może przyjąć stan, który nie odpowiada któremuś ze zdefiniowanych stanów. W trybie Save określony zostaje stan, który zostaje wywołany, gdy automat straci synchronizacje. Jak wskazuje nazwa szybszym rozwiązaniem jest tryb Fast

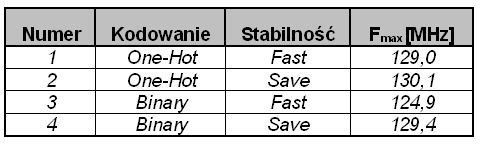

W przypadku projektowanego modelu przykładowego częstościomierza wykazały, że najszybciej działającą maszyną stanów Moore’a jest konfiguracja nr 3 w tabeli:

Maksymalna częstotliwość pracy maszyny stanów

Ze względu na niewielkie rozmiary maszyny stanów różnice są niewielkie. Można jednak stwierdzić, że wprawdzie kodowanie One-Hot jest szybsze od Binary, to jednak układ działa szybciej przy teoretycznie wolniejszym trybie Save.

Użycie w projekcie maszyny stanów znacznie ułatwia proces projektowania. Ważne jednak jest aby poprawnie wybrać maszynę stanów i jej konfigurację. Wybór właściwego rozwiązania z pewnością ułatwi przeprowadzenie kilu testów wybranych kombinacji.