ICS Simulator

ICS Symulator jest projektem badawczym obejmującym opracowanie metody emulacji sprzętowej implementacji użytkownika dla układów FPGA. Potrzeba dostarczenia takiego rozwiązania wynika z ograniczenia mocy obliczeniowej obecnych komputerów PC używanych do symulacji programowej. Dla przykładu, symulacja sprzętowego dekodera dźwięku MP3 zajmuje na komputerze dziesiątki minut dla każdego z utworów. W przypadku symulatora sprzętowego odbywa się to w czasie nawet i wielokrotnie szybszym niż czas odtworzenia tego utworu w czasie rzeczywistym. W czym więc problem aby zawsze tak symulować projekty? Problem pojawia się gdy w sprzęcie, czyli układzie FPGA chcemy podglądnąć stan poszczególnych sygnałów. Normalnie jest to bardzo utrudnione, a już na pewno wymagany jest dodatkowy cenny czas który należy skrócić do minimum. W tym celu powstał opisany tu symulator. Innowacyjność tego projektu badawczego polega na opracowaniu metody, która w przeciwieństwie do innych rozwiązań, umożliwia podgląd wszystkich sygnałów przy założeniu, że proces syntezy, implementacji i generacji plików wynikowych odbywa się tylko raz! Oczywistym bowiem jest, że jedną z podstawowych metod jest podpięcie na poziomie syntezy lub EDIF’a odpowiednich multiplekserów, które poprzez dedykowany interfejs dostarczają informacji o stanie wybranych przez użytkownika sygnałów. Niestety taka metoda wymaga wykonania przynajmniej pełnej implementacji modelu, co dla układu Spartan® użytego w ICS32sx może zajmować dziesiątki minut. Oczywiście opracowana tu metoda jest możliwa do zaimplementowana w wielokrotnie większych układach FPGA, gdzie czas wyboru nowych sygnałów do obserwacji, a co za tym idzie czas implementacji, jest wielokrotnie dłuższy.

Podstawowe cechy projektu:

- Niewielkie wydłużenie procesu syntezy, implementacji i generacji plików wynikowych. Dla największych projektów zawierających setki tysięcy sygnałów (bitów do obserwacji) czas dodatkowy generowania projektu obejmuje pojedyncze minuty. Czas wyboru nowych sygnałów jest znacznie krótszy

- Niewielki narzut na dodatkowe zasoby układu FPGA. Ze względu na automatyzację niektórych procesów, w niektórych przypadkach mechanizm debugowania sygnałów jest dla użytkownika zupełnie niewidoczny

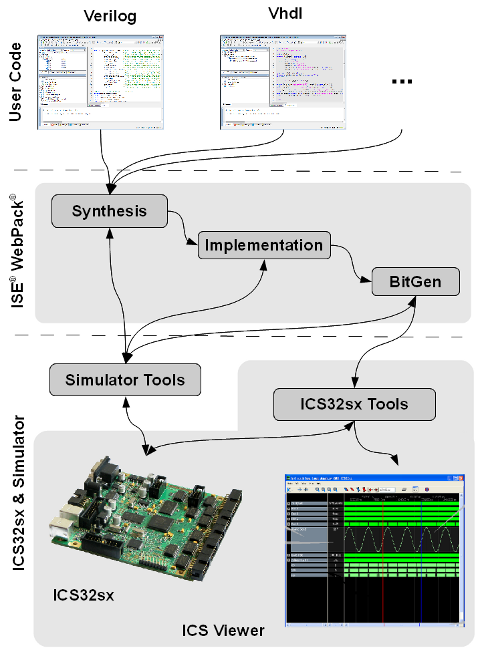

Zasada działania sytemu bardzo ogólnie zostanie wyjaśniona na przykładzie rysunku:

Opis

- Użytkownik w oparciu o swój kod źródłowy oparty o Verilog lub VHDL wykonuje kolejne kroki kompilacji w darmowym narzędziu firmy Xilinx ISE WebPack® . W celu otrzymania tzw. pliku bit wymagane jest wykonanie syntezy, implementacji oraz na końcu generacji pliku bit, który to plik jest jednym z formatów akceptowanych przez układy FPGA

- Na poszczególnych etapach kompilacji wymagane jest wprowadzenie odpowiednich ustawień w narzędziach firmy Xilinx® oraz konieczne jest wykonanie skryptów oferowanych przez opracowany symulator

- W końcowej fazie, po wgraniu implementacji do układu FPGA, użytkownik zyskuje możliwość podglądu praktycznie wszystkich sygnałów projektu. Podgląd ten realizowany może być:

- Tekstowo. Gdy wymagana jest analiza jednego stanu układu

- Graficznie. Gdy tekstowe przeglądanie waveform'u jest mało czytelne