Optymalizacja ustawień w układach FPGA

W przypadku układów FPGA dużo większe wyzwanie stanowi problem optymalizacji czasowej niż problem optymalizacji powierzchniowej. W przypadku produkcji małoseryjnej, na ogół kupowany układ FPGA posiada większą ilość cel niż wymaga tego realizowany projekt. Dzięki temu, łatwiej jest rozszerzyć funkcjonalność urządzenia oraz łatwiej jest narzędziom do implementacji umieścić projekt w wewnętrznych strukturach układu.

W przypadku projektowania struktur krzemowych znaczenie mają oba ograniczenia. O ile przyczyna ograniczeń czasowych dla układów scalonych wynika z wymagań jakie są stawiane dostępnej technologii, to w przypadku powierzchni, układy te projektowane są „na miarę”. Każda nawet najmniejsza nadwyżka powierzchni krzemu przekłada się na większy koszt gotowego układu scalonego.

Dla układów FPGA proces optymalizacji zarówno czasowej jak i powierzchniowej można podzielić na dwa etapy:

- Optymalizacja algorytmów użytych w modelu

- Optymalizacja ustawienia dostępnych w narzędziach do syntezy i implementacji

Pierwszy typ optymalizacji został opisany w artykule: Optymalizacja algorytmów w układach FPGA

W przypadku optymalizacji ustawień przedstawione zostaną najważniejsze metody używane do poprawienia wydajności projektowanego modelu.

Optymalizacja ustawień w narzędziach do syntezy i implementacji

Nawet najbardziej wymyślne algorytmy bez odpowiedniego wsparcia ze strony narzędzi do syntezy i implementacji mogą mieć bardzo słabe końcowe parametry powierzchniowe i czasowe.

Domyślna konfiguracja narzędzia WebPACK 9.2 firmy Xilinx jest ustawiona na generowanie optymalnych pod każdym względem modeli. Jednak wiadomo, każda optymalizacja może być bardziej nastawiona na rozmiar lub na prędkość działania. Ta podstawowa zasada powoduje, że już na wstępie istnieje możliwość poprawienia interesującego nas parametru projektowanego układu.

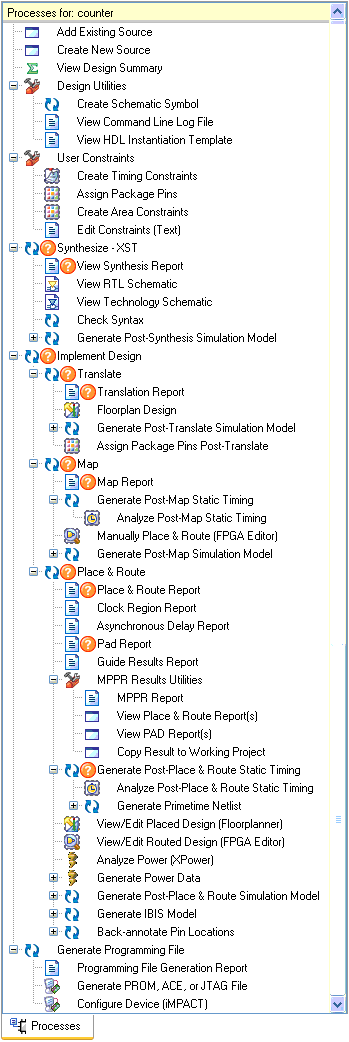

Poniżej przedstawiono widok panelu sterownia programu ISE WebPack:

Panel programu WebPACK

Aby bardzo dobrze dostroić narzędzie WebPACK należy koniecznie zapoznać się z bogatą dokumentacją oferowaną przez firmę Xilinx. Opis ustawień oparto o wersję 9.2 pomimo że obecnie dostępne są dużo nowsze wersje tego oprogramowania. Nie stanowi to jednak problemu ponieważ opisana optymalizacja nadal ma zastosowanie w nowszych wersjach programu.

Najprostszą metodą wyboru sposobu optymalizacji jest wybranie z menu programu odpowiedniej opcji dostępnej w miejscu:

Menu-> Project → Design Goals & Strategies

Można jednak samodzielnie uaktywnić opcje dostepne w panelu sterowania programu WebPack. Analizując domyślne ustawienia dla poszczególnych „Desin Goals & Strategies” można samodzielnie okreslić co wpływa na prędkość pracy modelu, co na rozmiar a co na redukcję pobieranej mocy.

W tym przypadku zostanie zwrócona uwaga wyłącznie na kilka bardzo ważnych ustawień, których pominięcie raczej nie jest zalecane.

Należą do nich:

- Optimization Effort and Strategy

- Timing Constraints

Optimization Effort and Strategy

Optimization Effort and Strategy. Jest to opcja, którą warto ustawić zarówno dla syntezy jak i implementacji. Ustawienia te dostępne są na panelu projektu przedstawionym na rysunku poniżej klikając prawym przyciskiem myszki na polach:

Synthesize-XST. (Category) Synthesis Option -> (Property Name) Optimization Effort. Ustawić na “High”

Map. (Category) Map Properties -> (Property Name) Optimization Strategy. Ustawić na “Speed”

Place & Router. (Category) Place & Route Properties -> (Property Name) Place & Route Effort Level. Ustawić na “High”

Po otwarciu właściwości danego pola należy przestawić styl wyświetlania na tryb „Advanced”

Timing Constraints

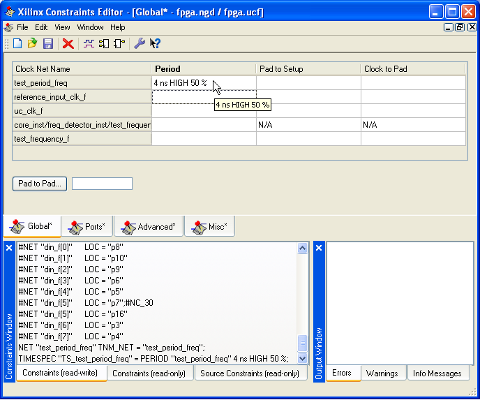

Timing Constraints. Jest to opcja, która informuje jaką częstotliwość pracy modułu spodziewamy się osiągnąć dla każdego z wejść zegarowych. Należy jednak pamiętać, że zbyt duża wartość wygeneruje błąd lub ostrzeżenie podczas wykonywania implementacji. Opcja ta jest dostępna na panelu projektu przedstawionym na rysunku

Panel programu WebPACK poprzez kliknięcie lewym przyciskiem myszki na pole:

Create Timing Constraints

W tym momencie wykona się synteza modelu oraz początkowa część implementacji. Gdy wszystko będzie przebiegać zgodnie z planem, pojawi się nowa aplikacja w której należy wybrać zakładkę Global i wprowadzić oczekiwaną wartość podaną w nanosekundach. Patrz rysunek poniżej. Bez tego parametru, narzędzie przestaje optymalizować układ dużo wcześniej niż umożliwiają mu na to jego algorytmy.

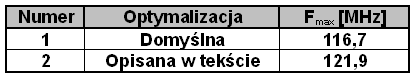

W przypadku modelu częstościomierza przed i po zastosowaniu opisanych ustawień narzędzia uzyskano następujące wyniki:

Maksymalna częstotliwość pracy modelu FPGA

Na podstawie danych z tabeli 3 można stwierdzić, że nawet dla prostego przykładowego modelu częstościomierza, który zajmuje bardzo mało zasobów układu FPGA, poprawa maksymalnej częstotliwości pracy jest zauważalna. Niekiedy jednak zaznaczenie opisanych ustawień powoduje, że przy kilku domenach zegarowych, interesująca nas domena zegarowa będzie pracowała wolniej niż przez załączeniem dodatkowych funkcji optymalizacyjnych. W większości przypadków zaproponowane ustawienia narzędzia powodują znaczne przyśpieszenie pracy projektowanego układu. Test na innym znacznie bardziej rozbudowanym modelu (Analizator Stanów Logicznych) wykazał, że maksymalna częstotliwość pracy wzrosła ze 140MHz dla domyślnych ustawień do 214MHz po załączeniu opisanych w tym rozdziale ustawień.

Narzędzie WebPACK jest darmowym oprogramowaniem. Istnieją również narzędzia innych firm, niestety już dostępne odpłatnie, które syntezują model do niekiedy znacznie wydajniejszej postaci niż robi to wbudowany w WebPACK syntezer. Warto o tym pamiętać przy projektowaniu profesjonalnych urządzeń opartych o układy FPGA.

Pozycje wykorzystane jako dodatkowe źródła informacji:

- [x] Dokumentacja programu ISE WebPack

Autorem artykułu jest mgr inż. Krzysztof Fijak